Moderne Elektronik erfordert Leiterplatten, die eine hervorragende Leistung liefern und gleichzeitig über lange Lebensdauern hinweg anspruchsvolle Betriebsbedingungen aushalten. Ingenieure und Produktdesigner suchen kontinuierlich nach Leiterplattendesign-Methoden, die gleichzeitig die Energieeffizienz und die mechanische Robustheit verbessern, ohne die Funktionalität zu beeinträchtigen. Das Verständnis darüber, welche konkreten Designansätze diese entscheidenden Eigenschaften unmittelbar beeinflussen, ermöglicht es Herstellern, zuverlässige und kosteneffiziente elektronische Systeme zu entwickeln, die die strengen Anforderungen der Branchen Automobil, Industrie, Medizin und Konsumelektronik erfüllen. anwendungen .

Die Auswahl der richtigen Leiterplattendesign-Techniken erfordert die Bewertung mehrerer miteinander verbundener Faktoren, darunter die Fähigkeiten zum thermischen Management, die Optimierung der Leiterbahngestaltung, die Wahl geeigneter Materialien, Strategien zur Platzierung von Komponenten sowie Methoden zur strukturellen Verstärkung. Jede Technik trägt in Abhängigkeit vom Anwendungsfall, der Betriebsumgebung und den konstruktiven Randbedingungen unterschiedlich zur Effizienz und Langzeitstabilität bei. Diese umfassende Untersuchung beleuchtet bewährte Leiterplattendesign-Techniken, die sich nachweislich sowohl auf die Betriebseffizienz als auch auf die langfristige Haltbarkeit positiv auswirken, und liefert Ingenieuren praktische Auswahlkriterien für fundierte Konstruktionsentscheidungen, die den spezifischen Projektanforderungen entsprechen.

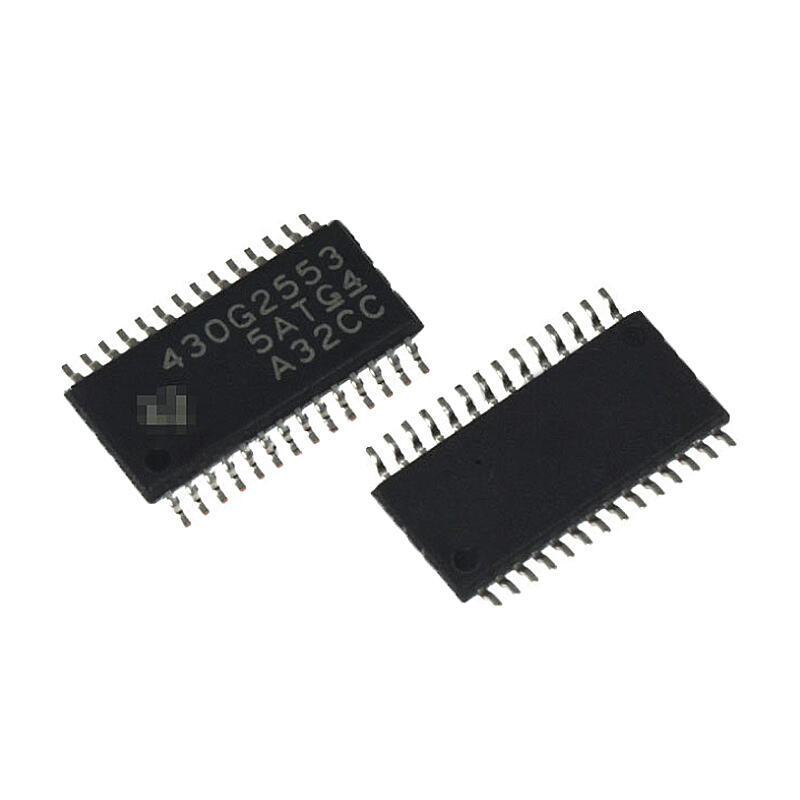

Die Implementierung dedizierter Versorgungs- und Masseebenen stellt eine der wirkungsvollsten Leiterplattendesign-Techniken zur Verbesserung sowohl der elektrischen Effizienz als auch der Signalintegrität dar. Eine sachgerechte Anordnung der Ebenen verringert die Impedanz in den Stromversorgungsnetzwerken, minimiert elektromagnetische Störungen und ermöglicht eine effektive Wärmeableitung über die gesamte Leiterplatte. Ingenieure sollten Versorgungsebenen unmittelbar benachbart zu Masseebenen positionieren, um eine niederinduktive Entkopplungskapazität zu erzeugen, die die Spannungsversorgung integrierter Schaltungen stabilisiert. Diese Konfiguration ist insbesondere für Hochgeschwindigkeits-Digitaldesigns und Mikrocontroller-Anwendungen von Vorteil, bei denen die Spannungsstabilität unmittelbar die Verarbeitungseffizienz und die Systemzuverlässigkeit beeinflusst.

Der Abstand zwischen den Versorgungs- und Masseebenen beeinflusst maßgeblich die Wirksamkeit der Entkopplung sowie die Eigenschaften der Wärmeableitung. Ein geringerer Abstand zwischen den Ebenen erhöht die interne Kapazität zwischen den Ebenen und verringert gleichzeitig die Schleifeninduktivität, was die transiente Antwort verbessert und den Spannungseinbruch während Stromspitzen reduziert. Allerdings beschränken die Fertigungsmöglichkeiten und die Eigenschaften des Dielektrikummaterials den technisch erreichbaren Mindestabstand. Die Abwägung dieser Faktoren erfordert die Auswahl geeigneter Kern- und Prepreg-Dicken, die sowohl die Anforderungen an die Impedanzsteuerung erfüllen als auch eine ausreichende mechanische Festigkeit gewährleisten, um Verzug und Delamination während thermischer Zyklen zu verhindern.

Die Organisation der Signallagen entsprechend Geschwindigkeits- und Empfindlichkeitsklassifizierungen optimiert die elektromagnetische Verträglichkeit und verringert Übersprechen, das die Signalqualität beeinträchtigt und den Stromverbrauch erhöht. Hochgeschwindigkeitssignale sollten auf Lagen geführt werden, die unmittelbar an Referenzebenen angrenzen, um eine konstante Impedanz zu gewährleisten und Unstetigkeiten im Rückführpfad zu minimieren. Diese Anordnung reduziert Strahlungsverluste und Reflexionen, die Energie verschwenden und Störgeräusche erzeugen. Die Trennung empfindlicher analoger Signale von störanfälligen digitalen Leitungen durch dedizierte Lagenzuweisungen verhindert Störungen, die die Messgenauigkeit beeinträchtigen und analoge Schaltungen zwingen, zusätzliche Leistung für die Rauschfilterung aufzuwenden.

Die Steuerung der Routing-Dichte über die Signallagen verhindert Engpässe, die einen übermäßigen Einsatz von Vias und längere Leiterbahnpfade erzwingen. Längere Signalleitungen erhöhen ohmsche Verluste, Ausbreitungsverzögerungen und die Anfälligkeit für mechanische Spannungen infolge thermischer Ausdehnung. Eine strategische Zuweisung der Lagen sorgt für ein Gleichgewicht zwischen Routing-Effizienz und elektrischen Leistungsanforderungen und stellt sicher, dass kritische Signale optimale Pfade verfolgen, während gleichzeitig ausreichender Abstand für die Dauerfestigkeit gewahrt bleibt. Diese Leiterplatten-Design-Techniken reduzieren insgesamt den Stromverbrauch durch minimierte Übertragungsverluste und verbessern die Zuverlässigkeit, indem sie mechanische Spannungskonzentrationen begrenzen, die Ausgangspunkt für Versagensmechanismen sind.

Die Auswahl geeigneter Kupfergewichte für verschiedene Leiterplattenschichten stellt eine grundlegende PCB-Design-Technik dar, die sich unmittelbar auf die thermische Leistung und die Stromtragfähigkeit auswirkt. Dickere Kupferschichten ermöglichen eine bessere Wärmeverteilung und geringere ohmsche Verluste, wodurch die Effizienz in Stromversorgungsnetzwerken und Hochstromschaltungen verbessert wird. Ingenieure geben üblicherweise 2 Unzen Kupfer für Stromversorgungsebenen und Hochstromleiterbahnen an, während Signalleiterschichten häufig 1 Unze Kupfer verwenden, um Leistung und Fertigungskosten in Einklang zu bringen. Die durch dickere Kupferschichten bereitgestellte thermische Masse erhöht zudem die Zuverlässigkeit, da Temperaturgradienten – welche Materialspannungen und Lotverbindungs-Ermüdung verursachen – reduziert werden.

Die strategische Kupferverteilung geht über einheitliche Lagenanforderungen hinaus und umfasst auch thermische Entlastungsmuster um Vias und Bauteil-Montagebereiche. Eine sachgerecht ausgelegte thermische Entlastung verhindert übermäßiges Wärmeableiten während des Lötvorgangs, bewahrt jedoch gleichzeitig eine ausreichende Stromtragfähigkeit und Wärmeleitung im Betrieb. Die Abwägung dieser konkurrierenden Anforderungen erfordert eine sorgfältige Analyse der Wärmeleitwege und Stromverteilungsmuster. Ingenieure müssen prüfen, ob eine erhöhte Kupferdicke in bestimmten Leiterplattenbereichen ausreichende Effizienz- und Haltbarkeitsverbesserungen bietet, um die zusätzlichen Fertigungskosten und Gewichtsbeschränkungen zu rechtfertigen.

Die Implementierung von thermischen Durchkontaktierungen (Vias) unter wärmeentwickelnden Komponenten schafft effiziente Leitungswege, die thermische Energie an interne Kupferlagen und externe Kühlkörper ableiten. Diese Leiterplattendesign-Technik senkt die Sperrschichttemperaturen in Leistungshalbleitern, Spannungsreglern und Verarbeitungseinheiten signifikant, was die Betriebseffizienz und Lebensdauer der Komponenten verbessert. Die Anzahl, der Durchmesser und das Anordnungsmuster der thermischen Vias bestimmen die Wirksamkeit des Wärmetransfers; engere Via-Abstände und größere Durchmesser führen im Allgemeinen zu einer besseren thermischen Leistung innerhalb der Grenzen der Fertigungsmöglichkeiten.

Die Anordnungsmuster der Durchkontaktierungen (Vias) müssen sowohl thermische als auch elektrische Anforderungen erfüllen, ohne die strukturelle Integrität zu beeinträchtigen. Dichte Via-Anordnungen können die mechanische Festigkeit beeinträchtigen, indem sie Spannungskonzentrationsstellen während des thermischen Zyklierens erzeugen, was möglicherweise Risse auslöst, die sich durch die Leiterplattenschichten fortpflanzen. Die Optimierung der Via-Verteilung stellt einen Kompromiss zwischen verbesserter Wärmeleitfähigkeit und Bedenken hinsichtlich der mechanischen Haltbarkeit dar; hierbei kommen häufig gestaffelte Muster zum Einsatz, die eine ausreichende Wärmeübertragung gewährleisten und gleichzeitig die Biegefestigkeit der Leiterplatte bewahren. Diese Überlegungen sind insbesondere bei Anwendungen von Bedeutung, die erheblichen Temperaturschwankungen ausgesetzt sind, da thermische Zyklierungsspannungen die Ermüdungsversagensmechanismen beschleunigen.

Die strategische Platzierung von Komponenten stellt eine der wichtigsten Leiterplattendesign-Techniken dar, die sowohl die thermische Effizienz als auch die Langzeitzuverlässigkeit beeinflussen. Die Gruppierung von Komponenten mit ähnlichen thermischen Eigenschaften erzeugt vorhersagbare Temperaturzonen, die das thermische Management vereinfachen und lokale Hotspots verhindern. Umgekehrt verhindert die Isolierung leistungsstarker Komponenten von temperatursensiblen Geräten thermische Interferenzen, die die Leistung beeinträchtigen und die Alterung beschleunigen. Stromversorgungsschaltungen, Motor-Treiber und Verarbeitungseinheiten erzeugen erhebliche Wärme, die benachbarte Komponenten beeinflusst; daher ist ein ausreichender Abstand sowie thermische Barrieren erforderlich, um optimale Betriebsbedingungen über die gesamte Leiterplatte hinweg sicherzustellen.

Bei der Platzierung müssen auch die Luftströmungsmuster und der Zugang zum Kühlkörper in der endgültigen Baugruppe berücksichtigt werden. Durch die Positionierung wärmeentwickelnder Komponenten dort, wo die Kühlluft in das Gehäuse eintritt, wird die Effizienz des konvektiven Wärmeübergangs maximiert und die Abhängigkeit von leitungsgebundenen Kühlwegen über die Leiterplatte verringert. Dieser Ansatz verbessert die Gesamteffizienz des Systems und reduziert gleichzeitig die thermische Belastung der Leiterplattenmaterialien und Lötverbindungen. Ingenieure sollten während der Optimierung der Komponentenplatzierung thermische Verteilungsmuster simulieren, um problematische Konfigurationen bereits vor der Freigabe für die Fertigung zu identifizieren, da eine Nachjustierung der Komponenten nach der Produktion kostspielig und zeitaufwändig ist.

Die Platzierung von Komponenten beeinflusst die mechanische Haltbarkeit erheblich, da sie die Spannungsverteilung auf der Leiterplatte während Handhabung, Montage und Betriebsbelastung bestimmt. Die Positionierung schwerer Komponenten in der Nähe der Leiterplatten-Stützpunkte minimiert Biegemomente, die zu Biegespannungen und möglichen Leiterbahnrissen führen. Große Komponenten, die sich in der Mitte der Leiterplatte oder an freitragenden Kanten befinden, weisen bei Stoß- und Vibrationsereignissen eine größere Durchbiegung auf, was die Belastung der Lötstellen erhöht und die Ermüdungsbruchentwicklung beschleunigt. Die Anwendung dieser Leiterplattendesign-Techniken erfordert die Analyse der erwarteten mechanischen Belastungsbedingungen sowie die Anpassung der Komponentenpositionen, um Spannungskonzentrationen zu minimieren.

Die Platzierung der Steckverbinder erfordert besondere Aufmerksamkeit, da die Kupplungskräfte und die Kabelzugbelastung erhebliche mechanische Lasten in die Leiterplattenbestückung einleiten. Die Montage von Steckverbindern in der Nähe von Leiterplattenrändern und Stützstrukturen verteilt die Einsteckkräfte effektiver und verringert so die Durchbiegung der Leiterplatte sowie die zyklische Belastung benachbarter Lötstellen. Eine Verstärkung der Leiterplattenbereiche um die Steckverbinder – beispielsweise durch zusätzliche Befestigungslöcher, Versteifungsrippen oder lokale Dickeerhöhungen – verbessert die Dauerfestigkeit weiter, insbesondere bei Anwendungen mit häufigen Verbindungsvorgängen oder Kabelbewegungen. Diese mechanischen Überlegungen ergänzen thermische Platzierungsstrategien, um Layouts zu erstellen, die sowohl Effizienz als auch Langzeitzuverlässigkeit optimieren.

Die Implementierung einer Routing-Methode mit kontrollierter Impedanz stellt eine wesentliche Leiterplattendesign-Technik für Hochgeschwindigkeitssignale dar, bei der Reflexionen und Überschwingungen Energie verschwenden und die Datenübertragung stören. Die Aufrechterhaltung einer konstanten Leitergeometrie relativ zu Referenzebenen erzeugt eine vorhersagbare charakteristische Impedanz, die an die Abschlussimpedanzen von Quelle und Last angepasst ist und dadurch Signalreflexionen minimiert, die eine erneute Übertragung erforderlich machen und den Stromverbrauch erhöhen. Für das Routing mit kontrollierter Impedanz sind präzise Spezifikationen hinsichtlich Leiterbreite und Leiterabstand erforderlich, die aus den Stackup-Parametern berechnet werden; dies erfordert eine enge Abstimmung mit den Fertigungsmöglichkeiten, um realisierbare Toleranzen sicherzustellen.

Die Optimierung der Leiterbahnbreite stellt einen Kompromiss zwischen elektrischer Leistung, Stromtragfähigkeit und Fertigungsbeschränkungen dar. Breitere Leiterbahnen verringern ohmsche Verluste und verbessern die Stromtragfähigkeit, beanspruchen jedoch mehr Platz auf der Leiterplatte und können an den Anschlussstellen von Bauelementen Impedanzsprünge verursachen. Ingenieure müssen geeignete Leiterbahnbreiten basierend auf den erwarteten Stromstärken, zulässigen Spannungsabfällen sowie Temperaturanstiegsgrenzen berechnen. Ein übermäßiger Temperaturanstieg in schmalen Leiterbahnen führt nicht nur zu einer Verschwendung elektrischer Leistung, sondern beschleunigt zudem die Alterung des Leiters und erhöht die thermische Belastung benachbarter Materialien, was langfristig die Zuverlässigkeit beeinträchtigen kann.

Die Steuerung der Rückführungswege für Ströme stellt eine häufig übersehene Leiterplattendesign-Technik dar, die sowohl die Effizienz als auch die elektromagnetische Leistungsfähigkeit erheblich beeinflusst. Hochfrequente Signalströme kehren über die nächstgelegene Referenzebene zurück, wobei sie den Weg mit geringstem Impedanzverlauf nehmen, der in der Regel direkt unter der Signalleitung verläuft. Die Aufrechterhaltung ununterbrochener Rückführungswege – etwa durch Vermeidung von Ebenentrennungen und Minimierung von Via-Übergängen – verringert die Schleifenfläche, reduziert Strahlungsverluste und verhindert Übersprechen zwischen benachbarten Signalen. Unterbrochene Rückführungswege zwingen die Ströme, längere Wege mit höherer Impedanz zu durchlaufen, was die Verlustleistung sowie die elektromagnetischen Emissionen erhöht.

Die Platzierung von Durchkontaktierungen entlang der Signalleitungen muss den Rückstromfluss berücksichtigen, um Impedanzsprünge zu vermeiden und die Signalintegrität aufrechtzuerhalten. Wenn Signale zwischen Schichten wechseln, benötigen die Rückströme nahegelegene Verbindungsdurchkontaktierungen (stitching vias), um dem Signalleitungswechsel ohne erhebliche Umwege zu folgen. Eine unzureichende Platzierung solcher Verbindungsdurchkontaktierungen erhöht die Induktivität des Rückstrompfads und führt dadurch zu Spannungstransienten, stärkeren elektromagnetischen Emissionen sowie Leistungsverlusten. Eine gezielte Platzierung von Durchkontaktierungen in der Nähe von Schichtübergängen gewährleistet niederohmige Rückstrompfade, die die Signalqualität bewahren und parasitäre Effekte minimieren, welche die Effizienz beeinträchtigen. Diese Routing-Überlegungen wirken sich unmittelbar auf den Stromverbrauch hochgeschwindigkeitsdigitaler Systeme aus, da Signalintegritätsprobleme eine Erhöhung der Treiberstärke sowie einen größeren Aufwand für Fehlerkorrektur erforderlich machen.

Die Auswahl geeigneter Substratmaterialien bestimmt grundlegend die thermischen, elektrischen und mechanischen Leistungsmerkmale einer Leiterplatte (PCB). Standard-FR-4-Materialien bieten für die meisten Anwendungen eine ausreichende Leistung; für Hochzuverlässigkeitsdesigns können jedoch verbesserte Materialien mit höherer Wärmeleitfähigkeit, niedrigeren Verlustfaktoren oder besserer Dimensionsstabilität erforderlich sein. Laminatwerkstoffe mit hoher Wärmeleitfähigkeit verringern Temperaturgradienten und verbessern die Effizienz der Wärmeableitung – insbesondere vorteilhaft in Leistungselektronik und dicht bestückten Leiterplatten. Diese Materialien sind in der Regel teurer als Standard-FR-4, bieten aber Effizienz- und Haltbarkeitsverbesserungen, die die zusätzlichen Investitionskosten bei anspruchsvollen Anwendungen rechtfertigen.

Die Glasübergangstemperatur (Tg) und der thermische Ausdehnungskoeffizient (CTE) des Materials beeinflussen entscheidend die Langzeitbeständigkeit bei Anwendungen mit thermischem Wechselbetrieb. Materialien mit höherer Tg bewahren ihre mechanischen Eigenschaften bei erhöhten Temperaturen und verhindern dadurch eine Aufweichung, die übermäßige Leiterplattenverformung und Spannungen im Via-Zylinder zur Folge hätte. Eine möglichst exakte CTE-Anpassung zwischen Substrat, Kupfer und Komponentenmaterialien minimiert die unterschiedliche Wärmeausdehnung, die bei Temperaturänderungen mechanische Spannungen erzeugt. Ingenieure müssen bei der Materialauswahl die betrieblichen Temperaturbereiche und die thermischen Wechselprofile bewerten, da ungeeignete Materialwahl die Versagensmechanismen beschleunigt – unabhängig von anderen in der Leiterplattendesign umgesetzten Maßnahmen.

Die Implementierung einer strukturellen Versteifung durch Optimierung der Plattdicke, Platzierung von Versteifungsrippen und Verteilung der Befestigungsbohrungen verbessert die mechanische Beständigkeit bei Anwendungen, die Schwingungen, Stößen oder Handhabungsbelastungen ausgesetzt sind. Eine Erhöhung der Plattdicke steigert die Biegesteifigkeit, verringert die Durchbiegung unter Last und schützt Lötverbindungen vor mechanischer Beanspruchung. Dickere Platinen erhöhen jedoch die Materialkosten, das Gewicht sowie das Bohrungs-Längen-Durchmesser-Verhältnis (Via-Aspect-Ratio), was die Fertigung erschwert. Ingenieure müssen daher die Steifigkeitsanforderungen mit praktischen Randbedingungen abwägen und setzen gegebenenfalls lokal begrenzte Dickeerhöhungen oder Versteifungsrippen ausschließlich in kritischen Bereichen ein, anstatt die Dicke flächendeckend zu erhöhen.

Die strategische Platzierung der Befestigungsbohrungen verteilt die Stützkräfte effektiv und minimiert gleichzeitig ungestützte Leiterplattenbereiche, die einer übermäßigen Verformung unterliegen. Die Analyse der erwarteten Lastbedingungen mittels Finite-Elemente-Modellierung identifiziert optimale Befestigungsstellen, die maximale Spannung und Durchbiegung minimieren. Zusätzliche Befestigungspunkte verbessern die mechanische Stabilität, erhöhen jedoch die Montagekomplexität und können die Platzierung von Komponenten einschränken. Diese Leiterplattendesign-Techniken erfordern eine iterative Bewertung, um optimale Konfigurationen zu erreichen, die sowohl die Anforderungen an die mechanische Dauerfestigkeit als auch die Fertigungspraktikabilität innerhalb der Projektvorgaben erfüllen.

Eine effiziente Panelisierung stellt eine häufig unterschätzte Leiterplattendesign-Technik dar, die sich auf die Fertigungsausbeute, die Kosten und die endgültige Platinenqualität auswirkt. Ein sachgerechtes Panel-Design optimiert die Materialausnutzung und bietet gleichzeitig ausreichende Stabilität während der Bearbeitungs- und Montageprozesse. Der Abstand zwischen den Leiterplatten innerhalb eines Panels muss für Fräswerkzeuge, Handhabungsvorrichtungen und Prüfeinrichtungen ausreichend bemessen sein, wobei gleichzeitig Materialverschwendung minimiert wird. Ein zu geringer Abstand erschwert die Handhabung und erhöht das Risiko von Beschädigungen, während ein zu großer Abstand Material verschwendet und die Fertigungseffizienz verringert. Die Integration von Ausbruchlaschen oder V-Nutungen zur Entpanelisierung erfordert eine sorgfältige Konstruktion, um mechanische Beschädigungen während der Trennung zu vermeiden und gleichzeitig während aller Montageschritte eine ausreichende Stabilität sicherzustellen.

Die Auswahl der Depaneling-Methode beeinflusst die endgültige Kantenqualität und mechanische Haltbarkeit der Leiterplatte. V-Schneiden erzeugt saubere Trennlinien, führt jedoch zu Mikrorissen, die sich unter Belastung ausbreiten und möglicherweise die Langzeitzuverlässigkeit beeinträchtigen. Beim Depaneling mit einer Fräsmaschine entstehen glattere Kanten ohne Mikrorisse, allerdings wird dabei Partikelkontamination verursacht, und es ist ein größerer Abstand zwischen den Leiterplatten für die Werkzeugfreigabe erforderlich. Ingenieure müssen die mechanischen Anforderungen der jeweiligen Anwendung sowie die Fähigkeiten des Montageprozesses bewerten, wenn sie eine Depaneling-Methode auswählen, da der Kantenzustand die Haltbarkeit direkt beeinflusst – insbesondere in Anwendungen, bei denen Leiterplatten in engen Gehäusen montiert oder an den Kanten belastet werden.

Die Implementierung eines geeigneten Lötstopplack-Designs und die Auswahl einer passenden Oberflächenfinish verbessern sowohl die Fertigungszuverlässigkeit als auch die Langzeitbeständigkeit. Die Aufbringung des Lötstopplacks schützt Kupferbahnen vor Oxidation, gewährleistet elektrische Isolation und definiert mit hoher Präzision die Lötstellen. Eine ausreichende Lötstopplackdicke sowie eine gute Haftung verhindern Unterschneidung und Abhebung, wodurch Kupfer freiliegt und korrosiven Umgebungen ausgesetzt wird. Die Lötstopplack-Ausdehnung um die Pads herum muss die Fertigungstoleranzen mit den elektrischen Freiräumen in Einklang bringen: Eine übermäßige Ausdehnung verringert die Kriechstrecken, während eine unzureichende Ausdehnung das Risiko von Kurzschlüssen während der Montage erhöht.

Die Auswahl der Oberflächenbeschaffenheit bestimmt die Lotbarkeit, die Lagerfähigkeit und den Kontaktwiderstand für freiliegende Kupferbereiche. Immersions-Silber, ENIG (Electroless Nickel Immersion Gold) und organische Lotbarkeitskonservierungsmittel bieten jeweils unterschiedliche Vorteile hinsichtlich Kosten, Lagerfähigkeit und elektrischer Leistung. ENIG bietet eine ausgezeichnete Haltbarkeit und Kontaktzuverlässigkeit für Pressfit-Steckverbinder und Anwendungen mit Gold-Drahtbondung, ist jedoch teurer als alternative Oberflächenbehandlungen. Diese PCB-Design-Techniken, die die Oberflächenbehandlung und -schutz beeinflussen, wirken sich unmittelbar auf die Langzeitzuverlässigkeit aus, indem sie Korrosion verhindern und die Integrität elektrischer Kontakte während der gesamten Betriebszeit bewahren – insbesondere in rauen Umgebungen mit extremen Temperaturen, hoher Luftfeuchtigkeit oder korrosiven Verunreinigungen.

Unterschiede hinsichtlich der Wirksamkeit von Leiterplattendesign-Techniken zur Effizienzsteigerung beruhen in erster Linie auf deren Einfluss auf ohmsche Verluste, thermisches Management und elektromagnetische Leistungsfähigkeit. Techniken, die sich direkt mit der Impedanz des Stromversorgungsnetzwerks befassen – beispielsweise dedizierte Versorgungsebenen und optimierte Kupferdicke – erzielen die deutlichsten Effizienzgewinne, indem sie Spannungseinbrüche und ohmsche Erwärmung reduzieren. Ebenso minimieren Routing mit kontrollierter Impedanz sowie eine sachgerechte Gestaltung der Rückführpfade für Ströme Signalintegritätsprobleme, die bei Hochgeschwindigkeitsdesigns zu einer erhöhten Sendeleistung und einem größeren Aufwand für Fehlerkorrektur führen. Die wirksamsten Techniken zielen jeweils auf die dominierenden Verlustmechanismen ab, die spezifisch für die jeweilige Anwendung sind, anstatt allgemeine Optimierungsansätze anzuwenden.

Umweltbedingungen beeinflussen grundlegend die Auswahl der Leiterplattendesign-Techniken, da sie die vorherrschenden Belastungsmechanismen und Ausfallmodi bestimmen. Hochtemperaturumgebungen erfordern ein verbessertes thermisches Management durch erhöhtes Kupfergewicht, thermische Durchkontaktierungen (Vias) und hochtemperaturbeständige Materialien (hoher Tg-Wert), die ihre Eigenschaften bei erhöhten Temperaturen bewahren. Anwendungen mit erheblichen Temperaturwechseln erfordern eine sorgfältige Abstimmung der Wärmeausdehnungskoeffizienten (CTE) der verwendeten Materialien sowie eine mechanische Verstärkung, um den Spannungen infolge unterschiedlicher Ausdehnung standzuhalten. Feuchte oder korrosive Umgebungen erfordern eine robuste Kompatibilität mit Konformbeschichtungen sowie eine sorgfältige Auswahl der Oberflächenfinishs, die Oxidation widerstehen. Ingenieure müssen die zu erwartenden Umweltbelastungen umfassend analysieren, um Design-Techniken entsprechend der jeweils größten Zuverlässigkeitsrisiken zu priorisieren.

Eine übermäßige Anwendung von Leiterplattendesign-Techniken ohne angemessene Analyse kann tatsächlich zu sinkenden Erträgen führen und unbeabsichtigte Folgen hervorrufen. So erhöht beispielsweise die Spezifikation unnötig dick beschichteter Kupferschichten die Kosten und die Fertigungskomplexität, ohne dass hierdurch bei moderaten thermischen Lasten ein entsprechender Leistungsgewinn erzielt wird. Ebenso verbraucht eine übertrieben aggressive Via-Stitching-Methode für Rückführpfade Routing-Ressourcen und kann durch übermäßige Platinenperforation die mechanische Integrität beeinträchtigen. Jede Design-Technik birgt Kompromisse hinsichtlich Kosten, Fertigbarkeit und physikalischer Randbedingungen, die stets anhand der konkreten Anforderungen bewertet werden müssen. Optimale Designs setzen Techniken gezielt dort ein, wo sie echte Leistungseinschränkungen beheben, statt sämtliche Parameter unabhängig von den jeweiligen Anwendungsanforderungen zu maximieren.

Die Design-Simulation bietet eine wesentliche Validierung von Leiterplattendesign-Methoden, indem sie elektrische, thermische und mechanische Leistungsmerkmale vor der Fertigung vorhersagt. Die Signalintegritätssimulation identifiziert Impedanzdiskontinuitäten, Übersprechen (Crosstalk) und Zeitverletzungen, die die Effizienz beeinträchtigen und Designkorrekturen erforderlich machen. Die thermische Simulation enthüllt Hotspots und Temperaturgradienten, die auf unzureichende Wärmeableitung oder Kühlmaßnahmen hinweisen. Die mechanische Finite-Elemente-Analyse prognostiziert Spannungskonzentrationen und Verformungen unter den erwarteten Lastbedingungen und validiert damit die ausreichende Auslegung struktureller Verstärkungen. Diese Simulationswerkzeuge ermöglichen eine iterative Optimierung der Design-Methoden mit quantitativer Leistungs-Rückmeldung und reduzieren dadurch das Entwicklungsrisiko erheblich sowie die Time-to-Market, indem Probleme bereits während der Designphase – und nicht erst nach der physischen Prototyperstellung – identifiziert werden.