現代の電子機器では、複数の電圧レールを制御し、エネルギー効率を最適化し、基板上の実装面積を最小限に抑えるため、ますます高度な電源管理ソリューションが求められています。複数出力型電源管理集積回路(通称:マルチアウトプットPMIC)は、こうした複雑な要件に対応する上で、家電製品、産業用機器、自動車システム、通信インフラストラクチャなど幅広い分野において不可欠なコンポーネントとして登場しました。これらの特殊な集積回路は、複数の電圧レギュレータ、電源スイッチ、および制御機能を単一パッケージに統合しており、エンジニアが現代の電子設計において電源分配アーキテクチャを構築する方法そのものを根本的に変革しています。

マルチアウトプットPMICが提供する利点は、単なる電力変換をはるかに超えており、システムの信頼性、熱性能、設計の柔軟性、および総所有コスト(TCO)の大幅な向上を含みます。これらの利点を理解することは、コンパクトな外形寸法、延長されたバッテリー駆動時間、および高度な機能性という厳しい市場要件を満たしつつ、電子システムを最適化しようとするハードウェア設計者、製品マネージャー、調達担当者にとって不可欠となります。本稿では、マルチアウトプットPMICが現代の電子機器の開発および展開において不可欠である理由となる具体的な利点について、包括的に検討します。

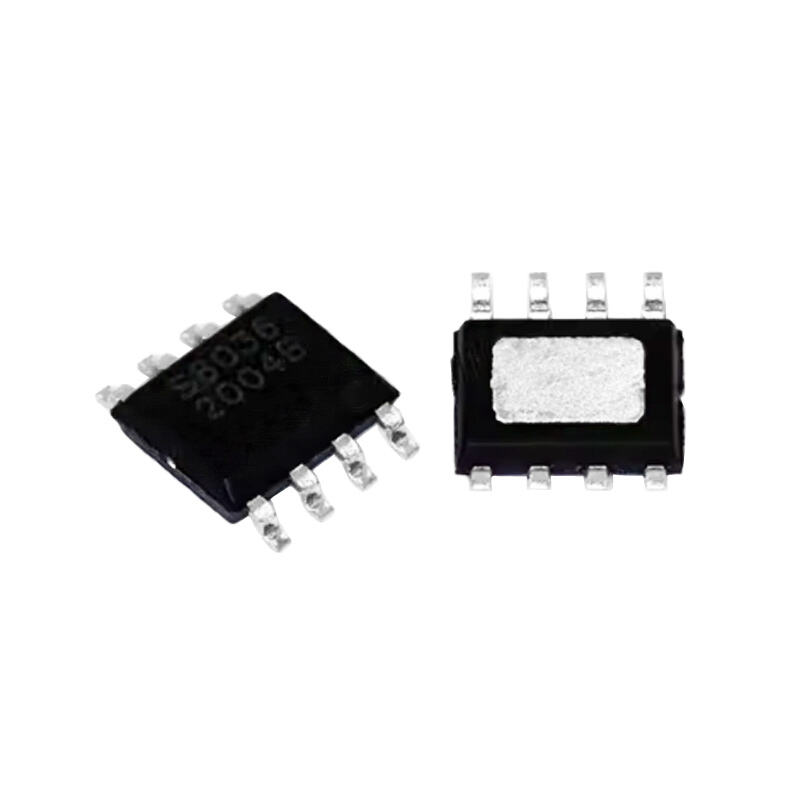

マルチアウトプットPMICの最も即座に明らかになる利点の一つは、電源管理回路に必要な物理的な実装面積を大幅に削減できる点にあります。従来のディスクリート電源設計では、各電圧レールごとに個別のレギュレータIC、インダクタ、コンデンサおよびサポート部品を別々に配置する必要があり、基板上の占有面積が非常に大きくなります。一方、マルチアウトプットPMICは複数の電圧レギュレータを単一パッケージ内に集積しており、冗長な部品を排除し、電源管理機能をコンパクトなソリューションへと統合します。これにより、ディスクリート実装と比較して、電源全体の実装面積を50~70%削減することが可能です。

この省スペース化は特に、 用途 ウェアラブルデバイス、スマートフォン、IoTセンサー、携帯型医療機器など、小型化が競争優位性をもたらす分野において、マルチ出力PMICは、貴重なPCB面積を解放することで、設計者が追加機能を搭載したり、バッテリー容量を増大させたり、製品全体の外形寸法を縮小したりすることを可能にします。統合型アプローチにより、基板レイアウトの複雑さも簡素化され、システム全体への電力供給に必要な電源プレーン数、配線層数、および相互接続数が削減されます。これは直接的に製造コストの低減と設計信頼性の向上につながります。

マルチ出力PMICは、統合アーキテクチャにより、優れた熱管理性能を実現します。PCB上で複数の個別レギュレータが独立して動作する場合、それぞれが局所的な発熱を引き起こし、個別に熱対策を講じる必要があり、システムの信頼性を損なう可能性のあるホットスポットが生じたり、追加の冷却インフラが必要になったりすることがあります。一方、マルチ出力PMICは、電源変換機能を単一の熱領域内に集約することで、共有熱経路による効率的な放熱、内蔵の熱遮断保護機能、および最適化されたパッケージ熱抵抗特性を可能にします。

高度なマルチ出力PMICは、動的熱制御、熱負荷を分散させるためのパワーステージの順序制御、およびアダプティブなパフォーマンス最適化を可能にする統合温度センサーなど、洗練された熱管理機能を備えています。これらの熱的優位性により、システムの動作温度範囲が拡大され、過酷な環境下での信頼性が向上し、外部ヒートシンクや強制空冷の必要性が低減または解消されます。また、統合された熱特性プロファイルは設計段階における熱解析を簡素化し、開発サイクルの短縮と、分散型ディスクリート電源を採用したシステムで問題となる熱関連の現場故障リスクの低減を実現します。

マルチ出力PMICは、システムの信頼性および運用安定性に直接影響を与える電源シーケンス制御および監視機能において、極めて重要な利点を提供します。FPGA、プロセッサ、メモリデバイス、周辺機器インタフェースなどを含む複雑な電子システムでは、ラッチアップ状態、データ破損、または部品の損傷を防止するために、電源投入および電源遮断の順序が厳密に制御される必要があります。マルチ出力PMICには、システム要件に応じて複数の電圧レールのタイミングおよび起動順序を調整するプログラマブルなシーケンスエンジンが内蔵されており、外部のシーケンスコントローラや複雑なディスクリート論理回路を用いずに、適切な初期化およびシャットダウンを保証します。

この統合型シーケンス機能により、独立したレギュレータを用いた場合に生じ得るタイミングの不確実性や、非協調的な起動特性に起因する電圧関係の問題が解消されます。 マルチ出力PMIC 通常、各出力レールを継続的に監視する電圧監視機能を備えており、いずれかの電圧が許容動作範囲から逸脱した場合にシステムリセットまたは保護シャットダウンを起動します。この包括的な電源整合性監視により、連鎖的障害が防止され、過電圧または低電圧状態から下流部品が保護され、高度な故障診断機能が実現されるため、トラブルシューティングが簡素化され、現場サービスコストが削減されます。

マルチアウトプットPMICの統合アーキテクチャは、複数の離散型電源を用いるシステムに内在するインターコネクションの複雑さを大幅に低減します。各離散型レギュレータには、入力電源接続、出力配線、フィードバック経路、イネーブル信号、およびグランドリターンが必要であり、これにより電圧降下、電磁妨害(EMI)、グランドループ問題を引き起こす可能性のある高密度な電力分配トレース網が形成されます。マルチアウトプットPMICは、共通の入力電源、グランド基準、および制御インターフェースを共有することにより、こうしたインターコネクション上の課題を最小限に抑え、寄生インダクタンスおよび寄生抵抗を低減したクリーンな電力分配ネットワークを実現します。

この簡略化された相互接続トポロジーにより、電源ノイズ特性および電磁両立性(EMC)が実測可能なレベルで向上します。電流経路が短縮されることで伝導性エミッションが低減され、過渡応答特性が改善されます。また、PMICパッケージ内に統合されたレイアウト最適化により、スイッチング段階間の磁気結合が最小限に抑えられ、クロストークや干渉の発生を防止します。マルチ出力PMICでは、複数の出力間で同期されたスイッチング周波数、EMIエネルギーを分散させるスプレッドスペクトラム変調、および統合フィルタリングといった高度な機能がしばしば採用されており、これらは外部フィルタ回路網の大幅な追加を必要とせず、基板面積や部品コストの増加を抑えたまま、ノイズ性能をさらに向上させます。

最新のマルチアウトプットPMICは、ハードウェア変更を必要とせずに、さまざまなシステム要件に応じて適応可能なプログラマブルな構成オプションを通じて、優れた設計柔軟性を提供します。多くのマルチアウトプットPMICには、デジタルでプログラマブルな出力電圧、電流制限、スイッチング周波数、および動作モードが備わっており、設計者はI2C、SPI、またはその他の標準通信インターフェースを用いてこれらを調整できます。このようなプログラマビリティにより、単一のPMIC設計で複数の製品バリエーションをサポートしたり、実際の動作条件に基づいてフィールドアップデートを行い性能を最適化したりすることが可能となり、BOM(部品表)の複雑さおよび在庫管理の課題を大幅に低減できます。

高度なマルチ出力PMICに内蔵されたアダプティブ電源管理機能は、単なる設定を超えて、動的電圧・周波数スケーリング(DVFS)、高効率モードと高速過渡応答モード間の自動モード切替、および負荷依存型最適化アルゴリズムを含みます。こうした知能的な機能により、システムはリアルタイムで電力効率と性能要件とのバランスを自動的に調整でき、携帯機器アプリケーションではバッテリー寿命を延長しつつ、ピーク需要時にも応答性を維持します。また、設計完了後の電源供給特性を微調整できる柔軟性により、予期せぬシステム間相互作用や仕様変更への対応に有効な余裕を確保でき、高コストなハードウェア改訂を回避できます。

マルチアウトプットPMICは、電源設計プロセスを簡素化し、開発の反復サイクルを短縮することで、大幅な市場投入期間短縮効果をもたらします。複数の分立型レギュレータを個別に設計するには、各電源レールごとに部品選定、安定性補償、熱管理、レイアウト最適化などについて詳細な検討が必要であり、多大な工学的リソースを要し、開発期間を延長させます。一方、マルチアウトプットPMICは、半導体メーカーにより包括的に検証済みの、アプリケーションに最適化された事前特性評価済みリファレンス設計を提供するため、設計者は最小限のカスタムエンジニアリングで実績のある電源アーキテクチャを実装できます。

マルチアウトプットPMICには、包括的なドキュメント、シミュレーションモデル、開発ツールが付属しており、不確実性を低減し、迅速なプロトタイピングを可能にすることで、設計サイクルをさらに加速します。多くのPMICメーカーは、評価ボード、設定用ソフトウェア、アプリケーションエンジニアリング支援を提供しており、設計者が電源性能を素早く検証し、特定のアプリケーション向けに設定を最適化することを支援します。こうした設計支援リソースから構成されるエコシステムにより、電源管理の実装に伴う技術的リスクが劇的に低減され、エンジニアリングチームは、マルチアウトプットPMICが既に実証済みの統合ソリューションで解決する基本的な電源課題への対応ではなく、製品の差別化要素へのリソース集中が可能になります。

マルチアウトプットPMICは、個別のディスクリートレギュレータと比較して単価が高くなる場合がありますが、すべての部品、組立工程、サプライチェーン関連要因を総合的に考慮した場合、システム全体のコストにおいて通常、著しいメリットをもたらします。単一のマルチアウトプットPMICにより、複数のレギュレータIC、多数の受動部品、および関連するサポート回路が置き換えられ、部品表(BOM)上の部品点数が大幅に削減されます。部品点数の削減は、直接的に調達コストの低減、在庫保有費用の削減、サプライヤー管理の簡素化、および生産計画を妨げる部品の供給不足リスクの軽減につながります。

アセンブリコストのメリットにより、マルチアウトプットPMICの経済的利点がさらに高まります。各部品の実装作業には、自動組立装置の稼働時間、検査要件、および潜在的な不良発生機会に起因するコストが発生します。複数のレギュレータを単一パッケージに統合することにより、マルチアウトプットPMICはピック・アンド・プレース作業回数、はんだ接合部の数、および検査ポイントを削減し、単位当たりの製造コストを低減するとともに、同時に製造歩留まりを向上させます。簡素化された組立工程は、製造の複雑さも軽減し、量産立ち上げのスピードアップや、より予測可能な製造能力計画の立案を可能にします。これは特に、単位コストが市場競争力に直結する高-volume向けコンシューマエレクトロニクス用途において極めて価値が高い特性です。

マルチ出力PMICは、単一ベンダーから単一品番で複数の電源管理機能を統合することにより、戦略的なサプライチェーン上の優位性を提供します。従来のディスクリート型電源実装では、複数のサプライヤーから部品を調達する必要があり、それぞれ異なる納期、最小注文数量、および在庫状況が存在します。このようなサプライチェーンの分断化は、調達プロセスの複雑化を招き、供給途絶への備えとして在庫コストを増加させ、生産遅延の発生リスクをもたらす複数のボトルネックポイントを生じさせます。マルチ出力PMICは、継続的なサプライヤーとの関係構築および資格認定プロセスを要する重要な電源部品の数を削減することで、ベンダー管理を簡素化します。

マルチ出力PMICによって実現される統合的な調達アプローチは、サプライヤーとの交渉における交渉力を高め、サプライチェーン全体の可視性を向上させます。数量の多い部品について少数のサプライヤーと取引を行うことで、通常、より有利な価格設定、技術サポートへのアクセス向上、および割り当て期間や生産能力制約時の迅速な対応が可能になります。さらに、単一のマルチ出力PMICの認定に要する検証作業は、複数の個別部品をそれぞれ認定する場合と比較して少なくて済み、新規設計の量産開始までの期間を短縮するとともに、部品の廃番やコスト最適化施策などに伴うサプライチェーンの調整が必要となった際の変更管理プロセスを簡素化します。

マルチアウトプットPMICは、集積設計の利点を活かしたアーキテクチャ最適化により、離散型レギュレータ実装と比較して優れたエネルギー効率を実現します。共用の入力段、共通の制御回路、および協調的なスイッチング戦略により、個別の離散型レギュレータでは発生する冗長な電力消費オーバーヘッドを最小限に抑えます。先進的なマルチアウトプットPMICでは、同期整流、最適化されたオン抵抗特性を備えた集積型パワーモスキット、および広範囲な負荷条件に応じて自動調整されるデッドタイム制御などの技術が採用されており、広い負荷範囲にわたって変換効率を最大化します。これにより、ポータブル機器におけるバッテリ駆動時間の延長、あるいは熱的に制約のあるシステムにおける発熱低減が直接的に実現されます。

多出力PMICの効率面での優位性は、多くの電子システムが長時間動作する軽負荷条件下で特に顕著になります。分立型電源レギュレータは、出力負荷に関係なく比較的一定の静止電流を維持するため、低電力レベルでは効率が低下します。一方、多出力PMICは、パルススキップ動作、バーストモードスイッチング、およびPWMとPFM変調方式間の自動切り替えといった高度な省電力モードを採用しており、マイクロアンペア級の負荷から定格最大電流まで、広範囲にわたって高効率を維持します。このような軽負荷時効率の最適化は、バッテリ駆動型IoTデバイス、ウェアラブル機器、常時起動(always-on)システムにおいて極めて重要であり、待機時の消費電力が実用可能なバッテリ寿命およびユーザー体験を直接左右します。

最新のマルチアウトプットPMIC(電源管理IC)には、リアルタイムのシステム動作条件に基づいてエネルギー消費を積極的に最適化する高度な電源管理機能が組み込まれています。ダイナミック・ボルテージ・スケーリング(DVS)などの機能により、プロセッサやその他のデジタル負荷は、低パフォーマンス時において電圧を低下させて動作させることができ、機能性を損なうことなく大幅な消費電力削減を実現します。マルチアウトプットPMICは、複数の電源レールにわたって電圧調整を同時に協調制御し、モバイル機器やアダプティブ型産業機器における典型的なユーザー操作パターンに特有の変動するワークロード条件下でも、各電源間の適切な電圧関係を維持しつつ、エネルギー効率の最大化を図ります。

高度なマルチアウトプットPMICに内蔵された負荷検出およびアダプティブ応答機能は、システムレベルでのエネルギー効率をさらに向上させます。これらのデバイスは、使用されていない電圧レールを自動的に無効化したり、現在の負荷レベルに応じてスイッチング周波数を調整して効率を最適化したり、負荷遷移を予測する先進的な電力管理アルゴリズムを実装することで、過渡状態におけるエネルギー損失を最小限に抑えます。また、マルチアウトプットPMICに統合されたモニタリング機能により、システムレベルのエネルギー分析が可能となり、消費電力パターンに関する可視性を提供します。これにより、ソフトウェア最適化の取り組みが支援され、アダプティブアルゴリズムが利用パターンを学習して能動的な電力管理を実現し、バッテリー寿命を延長しつつ、コンシューマーエレクトロニクス製品において応答性の高いユーザーエクスペリエンスを維持できます。

マルチ出力PMICは、適切な電圧レールのタイミング関係を保証する統合型電源シーケンシング、すべての出力における包括的な電圧監視および協調的な障害応答、および接続複雑性の低減(これにより潜在的な故障ポイントが排除される)を通じて信頼性を向上させます。また、単一パッケージによる統合は、分立部品の組み合わせと比較してより厳格な検証試験を実施します。さらに、各出力間で整合された熱的特性により、異なる熱応力条件下で個別レギュレータが異なる速度で劣化することに起因するタイミングドリフトや信頼性低下が防止されます。

マルチアウトプットPMICは、複数の個別レギュレータを独立して設計・補償・最適化する必要を排除する、事前に設計・検証済みのソリューションを提供することで、電源設計の複雑さを大幅に低減します。統合型アプローチにより、部品選定が簡素化され、必要な電源電子技術の専門知識が削減され、基板レイアウト上の課題が最小限に抑えられ、実績のある性能特性を備えた包括的なリファレンスデザインが提供されます。このような複雑さの低減は、開発期間の短縮、技術的リスクの軽減を実現し、エンジニアリングチームが電源実装という基本的な課題ではなく、アプリケーション固有の機能に集中できるようにします。

マルチ出力PMICは、産業用アプリケーションにおいて広範にわたって効果的に活用されており、現在市販されているデバイスでは、各レールにおける出力電流能力が数百mAから数Aに及び、高度な実装では総合出力電力が50Wを超えるものも存在します。産業向けマルチ出力PMICは、拡張温度範囲動作、強化された静電気放電(ESD)保護、自動車規格への適合性(automotive qualification standards compliance)、および過酷な運用環境に耐える堅牢なフォルトハンドリング機能を備えています。ただし、個々のPMICの能力を超える極めて高電力なアプリケーションでは、分立型ソリューションや、特定の高電流レール向けにマルチ出力PMICと外部パワーステージを組み合わせたハイブリッドアーキテクチャが必要となる場合があります。

現代のマルチアウトプットPMIC(電源管理IC)は、デジタルインタフェースを介して設定可能な出力電圧、効率向上またはEMI低減を目的としたスイッチング周波数の選択、ユーザー定義のタイミング関係による電源シーケンシングの構成、各出力レールごとの電流制限値の調整、および効率最適化モードと過渡応答最適化モードの間での動作モード選択など、広範な構成柔軟性を提供します。多くのデバイスでは、動作中のダイナミック再構成もサポートされており、ハードウェアの変更を伴わずにシステム要件の変化に応じて適応的な電源管理戦略を実現できます。これにより、製品ファミリ間での設計再利用性が極めて高まり、実際の展開環境に基づいてフィールドアップデートによって性能を最適化することも可能になります。